-

CordwainersCat

CordwainersCat

- 3060

- 6

- 0

- 0

hrk先生

@Prof_hrk

hrk先生

@Prof_hrk

Hotchips 1日目のTutorial. 今年はTutorialの日から沢山人が来ている。AI Chipが流行になっているためか? すぐ後ろにAndoさんがいる。

2019-08-19 01:22:40 hrk先生

@Prof_hrk

hrk先生

@Prof_hrk

Ntro = Nitro Card + Nitro security + Nitro Hypervisor。 Nitro card でVPC実現。でもTalkにTechnical Contentsはほぼない。。。

2019-08-19 01:58:11 hrk先生

@Prof_hrk

hrk先生

@Prof_hrk

次はMicrosoftのクラウドのアクセラレーション。Derek他がSpeaker. FPGA SolutionとASIC Solutionを説明する。 Cloudにおけるアクセラレーションは、特殊性がある。サーバサイズからの制限、I/O能力の制限、Powerの制限など。ファンのパワーも無視できない大きさ。

2019-08-19 02:22:18 hrk先生

@Prof_hrk

hrk先生

@Prof_hrk

アクセラレータの分類と説明は判りやすい。FPGA, ASIC, GPU. 新しいクラス分けとしてFixed Function, Programmableにわける。FPGAもLogicが固定だとProgrammableとは言えない。Circuit ProgrammableとInstruction Programmableの2個の軸で分類している。

2019-08-19 02:32:31 hrk先生

@Prof_hrk

hrk先生

@Prof_hrk

MicrosoftではこれをHybridなアプローチで加速する。例としてBrainWaveの話。FPGAベース。構造はTreeとしてBrainWave FPGAを繋いでいる。NPUはSoft NPU. RNNと1D+2D CNNに特化した命令の粒度を採用。命令のチェイニングが可能。 バンド幅問題は多数のFPGAのSRAM活用で解決する。

2019-08-19 02:39:29 hrk先生

@Prof_hrk

hrk先生

@Prof_hrk

FPGA内アーキは、Mtrix-Vector Multを並べる。この命令をチェインすることで効率を上げる。演算はMSFP8からMSFP11. 1bit sign, 5bit exponent, 2-5 bit mantissa. 96000MSFP8--FP8, 5760 --FP32 Stratix 10 280 de 49 TFLOPS, at 250 MHz. 早口過ぎて書くのが追い付かない。

2019-08-19 02:43:37 hrk先生

@Prof_hrk

hrk先生

@Prof_hrk

続いてSpeakerがSusan Carrieに変わりASIC アクセラレータのCorsicaの話。圧縮、暗号化、Authentiicationと暗号復号を担当。アーキテクチャはPCIE I/F, DMAエンジンの横に4個の圧縮・解凍パイプライン、暗号化・復号化のエンジンを付ける。CloudでASIC使うのは複数ユーザ、セキュリティ問題が難しい

2019-08-19 02:53:23 hrk先生

@Prof_hrk

hrk先生

@Prof_hrk

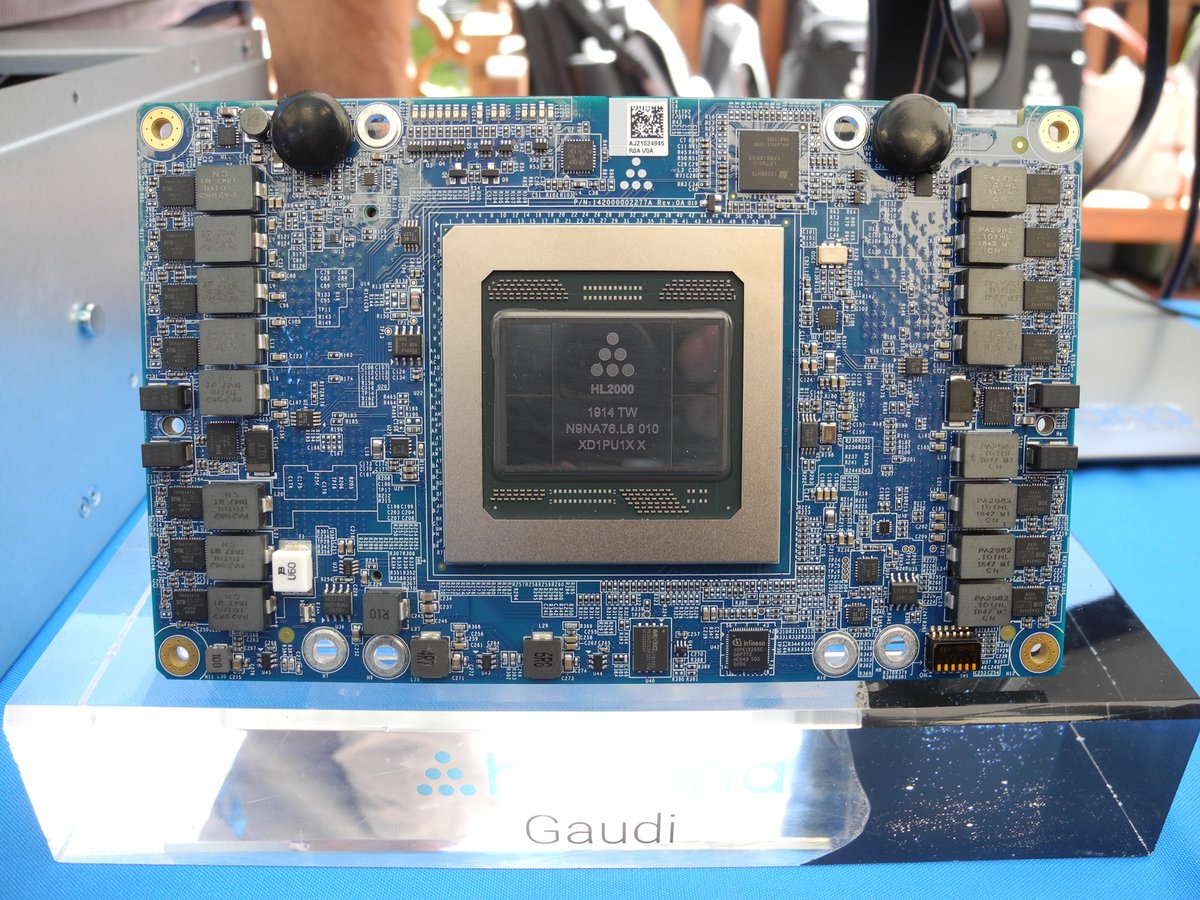

外にある展示デスクでHabanaのGaudiが展示してあった。学習用アクセラレータで、サーバに中二階のボードとして8枚させる。HBMが4枚使ったチップを使っている。興味深い。 pic.twitter.com/94kgiQhffJ

2019-08-19 03:50:00 拡大

拡大

拡大

拡大

hrk先生

@Prof_hrk

hrk先生

@Prof_hrk

次はGoogleのTPU. Software-Hardware co-designの話。TPUv1 2016.ISCA2017 に論文。 TPU v2 2017. 64GB HBMを使って2400GB/sバンド幅。32Lane PCIE Gen3. 何をCo-designと言っているか全然わからない。(HardwareがSoftからの要求を聞くだけではCo-designとは言えないだろう)

2019-08-19 03:55:23 hrk先生

@Prof_hrk

hrk先生

@Prof_hrk

Matrix Unitは3X3のシストリックアレイ。命令アクセス、レジスタファイルアクセス、制御へのエネルギーを減らすことで大きく効率化できる。FP32は必要なところだけ使い、あとは短い。Int16はLSTM-basedのアプリケーションで使う。Bfloat16ではExp7ビット、Mが7ビット。

2019-08-19 04:05:22 hrk先生

@Prof_hrk

hrk先生

@Prof_hrk

TPU v3では、ボードに4チップで水冷。420TFLOPS, 128GB HPM Memory. QSFP28ga 8 本ついている。これでCustom Interconnectを構成。 2Dトーラス、プロトコルは特製でスケーラブルに作れる。1ボードで11.5PFLOPS, 4TBメモリ。 インターコネクトの詳細は略されてしまった。

2019-08-19 04:13:10 hrk先生

@Prof_hrk

hrk先生

@Prof_hrk

午後のTutorialは全部RISC-Vについて。最初はAsanovic先生によるISAの解説。命題はなぜIntelはMobileチップがつくれないか&なぜARMはサーバ市場に食い込めないか。RISC-VのOpen ISAはそれを解決するという話。あとは全部この路線。全部の他のCPUをDisっている。ここは面白い。

2019-08-19 06:13:37 hrk先生

@Prof_hrk

hrk先生

@Prof_hrk

さすが大学のベテラン先生、話はとても面白い。RISC-VはOpen sourceではなく、Open Specificationと強調。何かかつてのTxxxの話で聞いた記憶がよみがえる。それのOpen sourceの組織、Commercial Coreの会社、Inhouse Coreの会社がある。ソフトウェアについても同様。

2019-08-19 06:22:46 hrk先生

@Prof_hrk

hrk先生

@Prof_hrk

続いてPart2.どこが違うのか? ・ISAが小さい ・USERと特権ISAのクリーンな分離 ・マイクロアーキテクチャやテクノロジ独立の仕様 ・ISAがモジュラーなので、拡張や特殊化が容易。可変長なので拡張できる。 ・Stableである。 ・コミュニティ・デザインである。 うーん、ますますアレに似ている。

2019-08-19 06:34:03 hrk先生

@Prof_hrk

hrk先生

@Prof_hrk

RISC-Vが仕様ベースの標準化ならば、UCBの影響力が強い少数のインプリの時期は良いが、もし広がるとすればバベルの塔は崩れるのじゃないかな?

2019-08-19 07:07:11 hrk先生

@Prof_hrk

hrk先生

@Prof_hrk

RISC-V Tutorial Part3はSoftwareのエコシステムについてSiFiveのBunnaroath Sou。GCCの-marchオプションで、RISC-Vないでのアーキテクチャ(32とか64とか)と命令Extensionを指定する。凄く種類が多い。アーキテクチャにない命令はエミュレーションコードを出力する。

2019-08-19 07:11:30 hrk先生

@Prof_hrk

hrk先生

@Prof_hrk

結局、Asanovic先生の会社であるSiFiveがRISC-Vをドミネートして栄えるかにRISC-Vの将来はかかっているが、それは元のアイディアと少し矛盾しているところが難しそう。 それにしてもSou氏は話べたで退屈だ。結構な人が寝ている。

2019-08-19 07:45:07 hrk先生

@Prof_hrk

hrk先生

@Prof_hrk

RISC-Vの次は、UCBのHoward Maoによるロボット用Rocket chipの話。沢山のパラメータを与えてSoC用の欲しいRISC-Vコアの設計を得るもの。企業ではSiFiveのE310, 大学ではUCB Hurricane-1. それをChiselというツールで作る。Scala上のチップを作るDSL.RTL記述を混ぜられる。

2019-08-19 08:35:17 hrk先生

@Prof_hrk

hrk先生

@Prof_hrk

Rocket chipはRISC-Vのマルチコアの下にバス、メモリ、I/OがつくSoC.バスは3個。システムバス、メモリバス、DMAデバイスがつながるバス。CoreはIn-order Single IssueのRISC-Vコア。LinuxがBoot出来る。L1のI,Dキャッシュを持つ。要するに普通のプロセッサコア。

2019-08-19 08:38:04 hrk先生

@Prof_hrk

hrk先生

@Prof_hrk

Howard MaoはUCBの大学院生。大学院生に主力開発を担わせるところも似ている。ここからSpeakerがJerry Zhaoにスイッチした。かれも院生。 BOOMはRISC-VのOoOコアでChiselで書かれている。3つの並行動作するユニット、あとは普通のOoO. RoCCはRISC-Vベースのアクセラレータ。命令拡張をしている

2019-08-19 08:45:49 hrk先生

@Prof_hrk

hrk先生

@Prof_hrk

RocketはVelilogシミュレーション、FPGAシミュレーションで検証している。それにSRAMマクロを加え、VLSIとしてGDSに食わせる。また、SoftwareへもChiselでコード出力する。研究への応用のところはちょっとわからないな。どのくらい動いているのか? 今動いているぷろじぇくとはChipyard, FireSIM

2019-08-19 08:55:01 hrk先生

@Prof_hrk

hrk先生

@Prof_hrk

BOOM, HAMMER、Chipyard, Hwacha(Vector Accelerator). 頑張っていると思うが、彼らが出たらどうするのだろうか。

2019-08-19 08:56:20